KAIST, 전기및전자공학부 김동준 교수 연구팀 플래시 전용 온-칩 네트워크 기술 적용 SSD 시스템 반도체 개발기존 시스템 대비 최대 31배 응답시간 줄이고 수명 23% 늘려

-

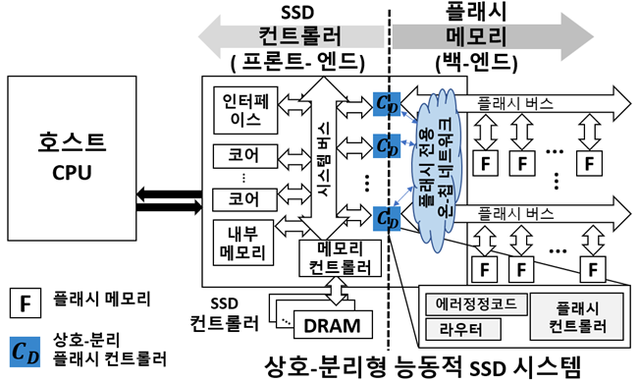

- ▲ KAIST 김동준 교수팀이 개발한 고성능 조립형 SSD 시스템 구조 모식도.ⓒKAIST

KAIST 전기및전자공학부 김동준 교수 연구팀이 고성능 조립형 SSD 시스템 개발을 통해 차세대 SSD의 읽기‧쓰기 성능을 비약적으로 높이고, SSD 수명연장에도 적용 가능한 SSD 시스템 반도체 구조를 세계 최초로 개발했다.김동준 교수 연구팀은 기존 SSD 설계가 갖는 상호-결합형 구조의 한계를 밝히고, CPU, GPU 등의 비메모리 시스템 반도체 설계에서 주로 활용되는 칩 내부에서 패킷-기반 데이터를 자유롭게 전송하는 온-칩 네트워크 기술을 바탕으로 SSD 내부에 플래시 메모리 전용 온-칩 네트워크를 구성함으로써 성능을 극대화하는 상호-분리형(de-coupled) 구조를 제안했다. 김 교수 연구팀은 이를 통해 SSD의 프론트-엔드 설계와 백-엔드 설계의 상호 의존도를 줄여 독립적으로 설계하고 조립 가능한 ‘조립형 SSD’를 개발했다.김 교수팀이 개발한 조립형 SSD 시스템 구조는 내부 구성요소 중 SSD 컨트롤러 내부, 플래시 메모리 인터페이스를 기점으로 CPU에 가까운 부분을 프론트-엔드(front-end), 플래시 메모리에 가까운 부분을 백-엔드(back-end)로 구분하고, 백-엔드의 플래시 컨트롤러 사이 간 데이터 이동이 가능한 플래시 메모리 전용 온-칩 네트워크를 새롭게 구성해, 성능 감소를 최소화하는 상호-분리형 구조를 제안했다.SSD를 구동하는 핵심 요소인 플래시 변환 계층의 일부 기능을 하드웨어로 가속, 플래시 메모리가 갖는 한계를 능동적으로 극복할 수 있는 계기를 마련했고 상호-분리형 구조는 플래시 변환 계층이 특정 플래시 메모리의 특성에 국한되지 않고, 프론트-엔드 설계와 백-엔드 설계를 독립적으로 수행하는 설계의 용이성을 가지는 점이 ‘조립형’ SSD 구조의 장점이다.기존 시스템 대비 응답시간을 31배 줄일 수 있었고 SSD 불량 블록 관리기법에도 적용해 약 23%의 SSD 수명을 연장할 수 있다.KAIST 전기및전자공학부 김지호 박사과정이 제1 저자, 전기및전자공학부 정명수 교수가 공동 저자로 참여한 이번 연구는 미국 플로리다주 올랜도에서 열리는 컴퓨터 구조 분야 최우수 국제 학술대회인 `제50회 국제 컴퓨터 구조 심포지엄’에서 오는 19일 발표될 예정이다.연구를 주도한 김동준 교수는 “이번 연구는 기존의 SSD가 가지는 구조적 한계를 규명했다는 점과 CPU와 같은 시스템 메모리 반도체 중심의 온-칩 네트워크 기술을 적용해 하드웨어가 능동적으로 필요한 일을 수행할 수 있다는 점에서 의의가 있으며 차세대 고성능 SSD 시장에 기여할 것으로 보인다. 상호-분리형 구조는 수명연장을 위해서도 능동적으로 동작하는 SSD 구조로써 그 가치가 성능에만 국한되지 않아 다양한 쓰임새를 가진다”며 연구의 의의를 설명했다.이번 연구는 컴퓨터 시스템 저장장치 분야의 저명한 연구자인 KAIST 정명수 교수와 컴퓨터 구조 및 인터커넥션 네트워크 (Interconnection Network) 분야의 권위자인 김동준 교수, 두 세계적인 연구자의 융합연구를 통해 이뤄낸 연구라는 의미가 있다고 관계자는 설명했다.한편 온-칩 네트워크(on-chip network): CPU·GPU등의 시스템 반도체 설계에 쓰이는 칩 내부의 요소에 대한 패킷-기반 연결구조를 말한다. 온-칩 네트워크는 고성능 시스템 반도체를 위한 필수적인 설계 요소중 하나로서 반도체칩의 규모가 증가할수록 더욱 중요해지는 특징이 있다.